### 2023 IEEE VLSI Review

연세대학교 전기및전자공학부 박사과정 한현호

# Session 04 Continuous-Time AD Converters Session 14 Nyquist-Rate ADCs

2023 IEEE VLSI의 ADC에 대한 내용은 Session 04와 Session 14에 각각 4편씩 실렸다. Session 04에서는 continuous-time ADC에 대해서 다루었다. 4편의 논문 중 3편이 continuous-time (CT) delta-sigma modulator (DSM)에 대한 내용이었으며 이 중 2편은 수백 MHz의 bandwidth로 동작하였다. 그리고 continuous-time ADC에서 가장 빠른 bandwidth를 갖는 논문은 time-interleaved를 사용한 pipelined ADC 였으며 1GHz의 bandwidth를 갖는다. Session 16에서는 1GHz의 bandwidth를 갖는 interleaved SAR ADC 1편과 수십 MHz bandwidth의 pipelined SAR ADC 2편 그리고 마지막으로 다른 논문에 비해서 속도는 2MHz bandwidth로 조금 느리지만 7nm CMOS 공정을 사용한 cyclic ADC가소개되었다. 이 글에서 각 session 마다 몇 개의 논문을 소개하려고 한다.

### #4-1 A 6.4-GS/s 1-GHz BW Continuous-Time Pipelined ADC with Time-Interleaved Sub-ADC-DAC Achieving 61.7-dB SNDR in 16-nm FinFET

5G 통신이 널리 사용됨에 따라 수 GHz bandwidth를 가지는 ADC의 필요성이 점점 중요해지고 있다. Discrete-time (DT) pipeline ADC는 수 GHz bandwidth를 달성하기 좋은 구조이지만 anti-alias filter가 추가적으로 필요하다는 단점을 가지고 있다. 반면에 CTDSM같은 경우에는 내재적인 anti-aliasing 특성으로 적은 면적을 차지 하지만 높은 oversampling ratio (OSR)가 필요하기 때문에 더 빠른 sampling frequency가 필요로 한다.하지만 CT pipeline ADC인 경우에는 수 GHZ의 bandwidth를 가지며 낮은 OSR과 내재된 anti-aliasing 특성으로 좋은 대안으로 보여진다. 기존의 CT pipeline ADC논문인 경우에는 multi-stage로 인해서 많은 파워 소모와 넓은 면적을 차지하였는데 이 논문에서는 VCO-based backend ADC를 활용하여 2개의 문제를 해결하였다. 그 결과 내재된 anti-aliasing 특성을 가지며 6.4GHz의 sampling frequency에서 3.2의 OSR(=1GHz)로 61.6dB의 SNDR, 240mW의 power 및 0.77mm²의 크기 그리고 157.9 dB의 FoMs을 달성하였다.

### #4-2 A 0.024mm<sup>2</sup> 84.2dB-SNDR 1MHz-BW 3rd-Order VCO-Based CTDSM with NS-SAR Quantizer (NSQ VCO CTDSM)

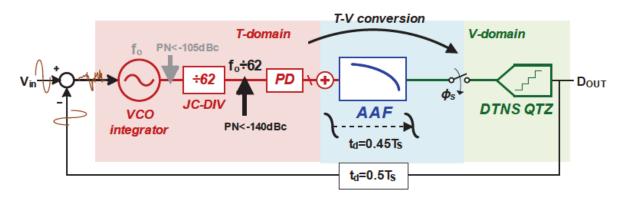

VCO 적분기는 CTDSM에서 작은 면적, 공정 친화성, saturation 되지 않는 적분 범위, 내재된 DWA의 이점으로 자주 사용된다. 하지만 이전의 논문들은 NTF의 차수가 대부분 2차로 한계가 있어 bandwidth와 resolution간의 tradeoff를 해결할 수 없었다. 이를 해결 하고자 VCO 여러 개를 cascade하여 사용할 수 있지만 linearization 과 stabilization에 있어 다소 어려운 점이 있다. 본 논문에서는 1차의 VCO frontend와 2차의 noise shaping (NS) SAR quantizer를 같이 사용하여 bandwidth와 resolution간의 tradeoff를 해결하면서 3차의 hybrid 구조를 만들었다. 1차의 VCO와 2차의 NSSAR를 연결하기 위하여 current-switching DAC anti-alias filter를 사용하였으며 면적을 줄이기 위해서 Johnson counter를 사용하였다. (그림 1). 그 결과 0.024mm²의 면적과 1MHz의 bandwidth 그리고 84.2dB의 SNDR로 기존의 VCO-based ADC중 면적대비 가장 높은 SNDR과 bandwidth 대비 가장 높은 SNDR를 각각 달성하였다.

[그림 1] Time to voltage AAF를 사용한 제안하는 구조

#### #14-1 A 2GS/s 11b 8x Interleaved ADC with 9.2 ENOB and 69.9dB SFDR in 28nm CMOS

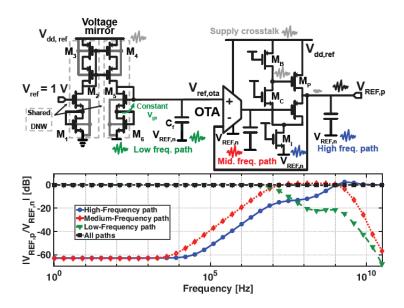

최근 통신 시스템은 60dB SNDR과 낮은 파워 소모를 유지하며 500MHz가 넘는 bandwidth를 가지는 ADC가 요구된다. Time interleaving 기술은 bandwidth를 높이는데 좋지만 채널간 mismatch로 인해 offset, gain, clock skew등이 문제가 된다. 또한 실 사용에서는 ADC의 성능저하를 막기위해서 입력 buffer를 사용해야만 한다. 이 논문에서는 voltage-mirrored flipped-voltage-follower (FVF) reference buffer를 사용하여 채널간 interaction을 최소로 설계하였다 (그림 2). 그 결과 2GHz의 sampling frequency에서 918MHz의 input을 넣어 57.3 dB의 SNDR과 69.9dB의 SFDR을 달성하였다. 또한 buffer를 포함하여 118.6mW의 파워 소모와 0.54 mm²의 면적을 달성하였다.

[그림 2] 제안하는 FVF reference buffer의 schematic 과 frequency response 시뮬레이션

## #14-4 A 0.75V 0.016mm<sup>2</sup> 12ENOB 7nm CMOS cyclic ADC with 1.5bit passive amplification stage and dynamic capacitance scaling

Multi-sensor 산업과 medical application 에서는 중간 정도의 conversion rate 와 high-resolution 를 가지면서 매우 작은 ADC 가 필요로 하다. 일반적으로 cyclic ADC 는 매우 작은 면적을 가질 수 있으나 scaling 을 하기 어렵다는 문제점을 가지고 있다. 이 논문에서는 이를 해결하여 7nm 공정에서 0.016mm2 의 매우 작은 면적과 12ENOB 의 매우 높은 resolution을 달성하였다.

#### 저자정보

#### 한현호 박사과정 대학원생

● 소속 : 연세대학교

● 연구분야: 임피던스 센서, VCO-based ADC

• 이메일 : hyunho912242@naver.com

• 홈페이지 : https://sites.google.com/site/ymsicl/